Ist die Kapazität des Kondensators immer gleich?

Multilayer ceramic capacitors (MLCCs) offer several advantages that make them a popular choice for various electronic applications, including high energy density, low cost, and a wide range of capacitance options. However, they are not without drawbacks, one of which is the capacitance reduction effect when subjected to a constant or DC voltage. This effect is commonly referred to as “DC bias” and information dedicated to this phenomenon can be found on manufacturers’ websites.

Unter Ingenieuren gilt die Faustregel, einen Kondensator mit einer Nennspannung zu verwenden, die 1,5 - 2-mal höher ist als die Betriebsspannung. In bestimmten Fällen, in denen eine maximale Optimierung der Stückliste erforderlich ist, könnte man sich jedoch fragen, ob es möglich ist, ein 16 V X5R MLCC in einer Schaltung mit einer Arbeitsspannung von 10 V zu verwenden. Was würde in einem solchen Szenario mit der Kapazität passieren? Wie unerwünscht wäre ihre Reduzierung?

Und was ist, wenn die Spannung nur für ein paar Sekunden ansteigt? In diesem Artikel werden wir uns mit den theoretischen Grundlagen dieses Problems befassen und praktische Lösungen untersuchen.

Die Ursache des Problems

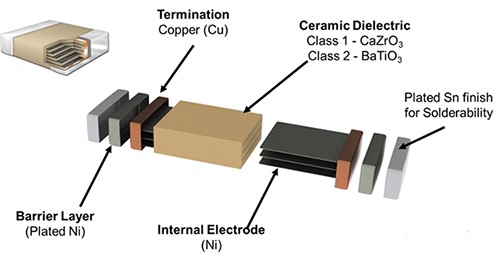

The issue lies with the material BaTiO3, which serves as the dielectric in capacitors. When subjected to an alternating voltage, dipoles in BaTiO3 can freely reorient under the influence of an electric field, providing capacitance for charge storage. However, when a DC voltage is present, a portion of the dipoles becomes “locked” and cannot fully reorient. This reduces the effective capacitance of the capacitor for noise suppression or ripple smoothing.

Abbildung 1 - Die Struktur des MLCC-Kondensators (Bildquelle: KEMET)

Gleichspannung und Herstellereinfluss

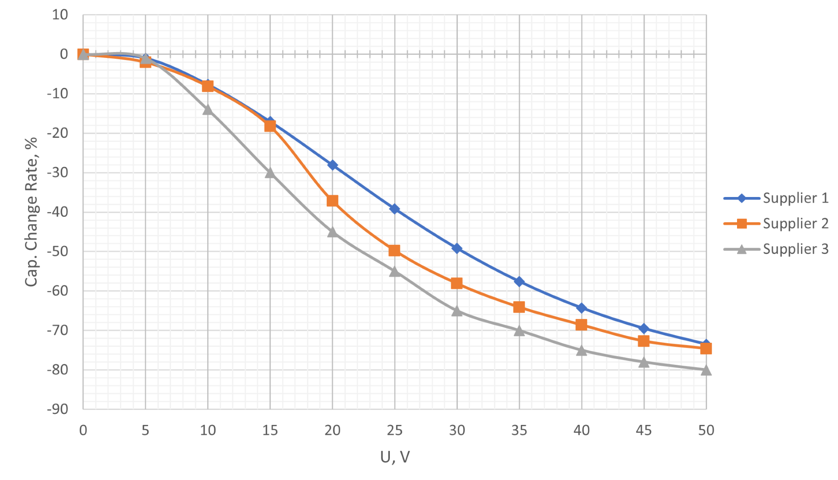

As mentioned earlier, increasing the DC voltage on the capacitor intensifies the locking of dipoles by the electric field. As a result, its capacitance decreases closer to the nominal voltage. The magnitude of this reduction depends on the manufacturer’s technology since each uses unique manufacturing methods. An example of such a reduction is shown below.

Figure 2 – Capacitance Loss with DC Bias on 1µF 50V X7R Capacitor in MLCC 0805 Package from Three Different suppliers.

Größe

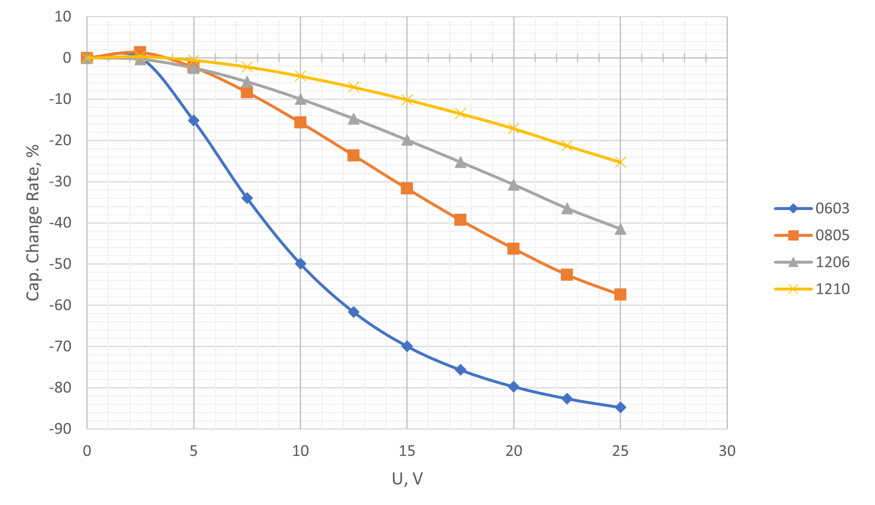

The capacitor’s size strongly influences its effective capacitance. Smaller dielectrics result in a higher percentage of dipoles being locked by the constant voltage, thereby intensifying the effect on capacitance. This means that the impact of voltage will vary for identical capacitors in different package sizes. An example is illustrated for 1µF ±10% X7R 25V capacitors in various packages.

Figure 3 – Capacitance Loss with DC Bias on 1µF 50V X7R Capacitor in different packages.

Dielektrika

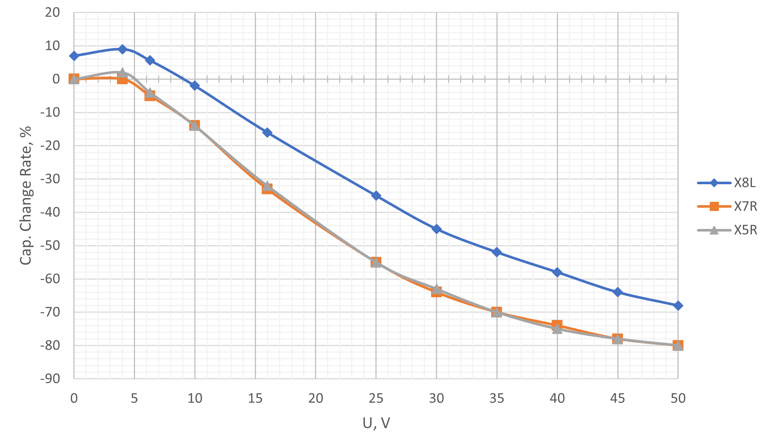

Die Verwendung eines höherwertigen Dielektrikums ist eine Möglichkeit, die effektive Kapazität zu erhalten. Dielektrika der ersten Klasse (NP0, C0G) beseitigen Probleme mit Gleichstromvorspannung. Solche Dielektrika sind jedoch teuer und in der Regel für kritische Anwendungen reserviert. Häufiger verwendet werden zweitklassige Dielektrika wie X8L, X7R, X5R usw. Abbildung 4 zeigt, wie die Gleichstromvorspannung je nach Dielektrikumstyp variiert, auch wenn verschiedene Dielektrikumstypen in einigen Fällen ähnliche Vorspannungswerte aufweisen können.

Figure 4 – Capacitance Loss with DC Bias on 1µF 50V 0805 Capacitor in different dielectrics.

Kapazität

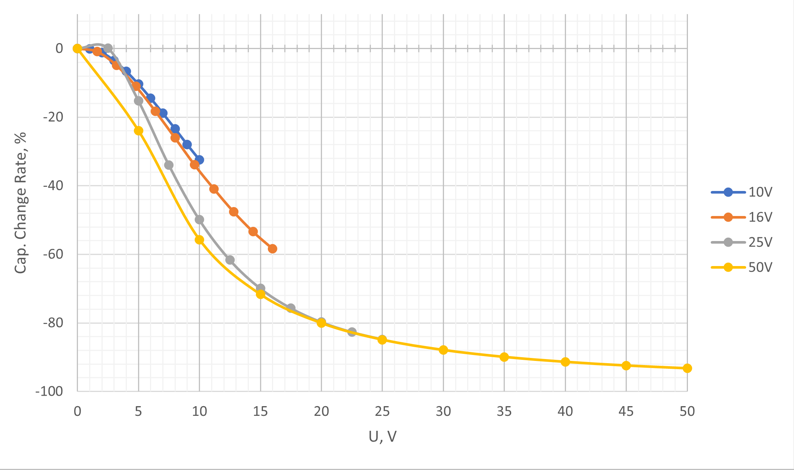

Auf den ersten Blick könnte man meinen, dass die Verwendung eines Kondensators mit einem höheren Kapazitätswert zu einer höheren effektiven Kapazität führen würde. Dies ist jedoch nicht immer der Fall. Manchmal kann ein Kondensator mit einer höheren Kapazität eine stärkere Reduzierung erfahren. Das liegt daran, dass eine höhere Kapazität bei gleicher Gehäusegröße zu einer höheren Dichte von Dipolen pro Volumeneinheit führt. Folglich wird bei gleichem elektrischem Feld (d. h. bei angelegter konstanter Spannung) eine größere Anzahl von Dipolen verriegelt, das führt zu einer geringeren effektiven Kapazität. Abbildung 5 zeigt ein solches Verhalten für 1µF ±10 % X7R-Kondensatoren im 0603-Gehäuse mit unterschiedlichen Nennspannungen.

Figure 5 – Capacitance Loss with DC Bias on 1µF 50V X7R 0603 Capacitor in different dielectrics.

Zeit

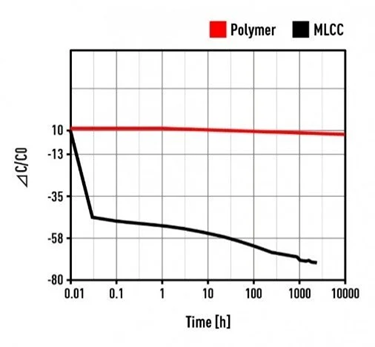

The voltage drop does not occur instantaneously, and it takes some time for the dipoles to become “locked.” It is essential to understand this to avoid fearing a capacitance decrease due to short-duration voltage spikes. According to the graph in Figure 6, the most significant capacitance drop occurs within the first 1-3 minutes. However, it does not stop there; the reduction continues even after an hour, two hours, or even 100 hours.

Figure 6 – Capacitance drop with time under DC Voltage BIAS (Image source: Panasonic)

Schlussfolgerungen

Zusammenfassend können wir die wichtigsten Methoden zur Erhaltung der effektiven Kapazität hervorheben:

• Verwendung einer größeren Packungsgröße

• Verwendung von hochwertigen Dielektrika

• Verwendung von Kondensatoren mit höheren Spannungswerten

• Verwendung von Kondensatoren mit einem geringen Spielraum bei der Nennkapazität

Nevertheless, each of these rules has exceptions, which is why, at DigitalGate, we always verify the DC Bias for each capacitor on the manufacturer’s website during the design phase to ensure our clients’ devices operate without any issues. By being mindful of the impact of DC Bias and employing appropriate mitigation strategies, engineers can optimize their electronic designs for improved performance and reliability.

Über den Autor:

Vladislav Mokluza ist ein Hardware-Ingenieur, der sich auf Schaltkreisdesign und PCB-Entwicklung in DigitalGate spezialisiert hat. DigitalGate bietet innovative Hardware- und Software-Entwicklungsdienstleistungen für modernste eingebettete Systeme an, die den Qualitätsstandards der jeweiligen Branchen entsprechen. Da wir ein flexibles und wettbewerbsfähiges Unternehmen sind, haben wir Kunden in der ganzen Welt, insbesondere in Nordamerika, Europa und Asien.